Single Event Upsets

Ionizing radiation is capable of inducing undesired effects in most silicon devices. A single event upset (SEU), is an unintentional change of state caused by ionizing radiation in any integrated circuit, including ASIC, ASSP, FPGA, memory, logic, and mixed-signal devices.

Xilinx devices are designed to have an inherently low susceptibility to SEUs. Although SEUs are extremely rare and fully recoverable in Xilinx devices, Xilinx understands the need for the utmost in system reliability and availability, and that managing SEUs requires far more than simply estimating SEU Failures-In-Time (FIT). To that end, Xilinx provides system designers a comprehensive solution for SEU mitigation.

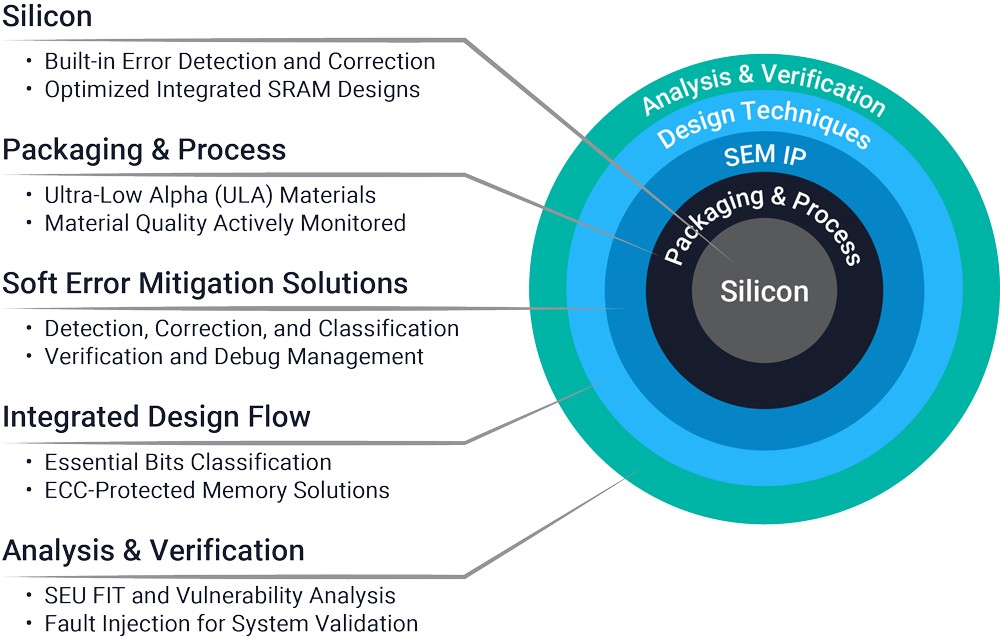

Xilinx SEU Solution

Silicon

The foundation of reliability and availability is the silicon. Through continued innovation in circuit design and layout techniques, Xilinx has lowered the intrinsic SEU FIT of the silicon with each new generation, enabling most application deployments without any additional SEU mitigation. In addition, should an SEU occur, Xilinx provides rapid embedded error detection and correction that can restore the device state, such that the majority of SEUs will not result in system interruption.

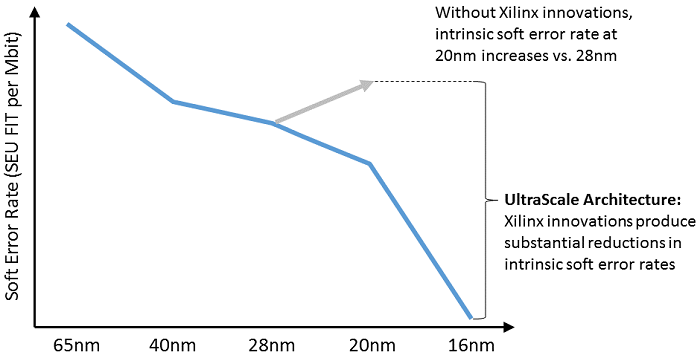

Xilinx SEU FIT Trend

To maximize the integrity of designs in UltraScale devices, Xilinx offers industry-leading resilience to SEUs through more than 40 techniques spanning process, layout, circuit, and device architecture. Compared to 7 Series devices, UltraScale devices achieve up to a 3x reduction in SEU FIT.

UltraScale+ devices are the next step in Xilinx's continuing efforts to offer the most robust and comprehensive solution available. UltraScale+ devices contain additional design innovations and use FinFET transistor technology as a multiplier to gain substantial additional reduction in SEU FIT. Most applications will meet their reliability and availability requirements based on the inherent resilience of UltraScale+ devices without any additional SEU mitigation.

Packaging

Xilinx uses only ultra-low alpha (ULA) packaging materials and actively monitors material suppliers to ensure compliance with ULA specifications.

Mitigation IP

To effectively manage SEUs, Xilinx offers free IP that can be leveraged to increase reliability and availability in applications requiring additional mitigation.

The Soft Error Mitigation (SEM) IP core is an automatically configured, pre-verified solution to detect, correct, and classify SEUs in Configuration RAM of Xilinx devices. The SEM IP core does not prevent SEUs; however, it provides a method to better manage their system-level effects. Proper management of SEUs increases reliability and availability, and reduces system maintenance and downtime costs. The SEM IP core remains in pre-production status until it has been fully tested and qualified through accelerated particle testing at a radiation effects facility.

Additionally, the Block Memory Generator IP core and FIFO Generator IP core provide optimized solutions for common memory structures, with flow-through error correcting code (ECC) support to virtually eliminate the effects of SEUs in BlockRAM and UltraRAM resources. The Memory Interface Solutions (MIS) IP core similarly provides flow-through ECC support for external DDR3 and DDR4 SDRAM memory systems.

Design Techniques

For applications demanding absolute safety or data integrity, Xilinx offers tools to assist in protection of critical design modules. The Isolation Design Flow (IDF) provides fault containment at the module level, enabling single-chip fault tolerance through supporting techniques such as redundancy, watchdog alarms, and logic segregation.

While optimization by EDA tools typically improves quality of results, these tools may also optimize away design-level SEU mitigation, such as redundant circuits or modules. Xilinx offers tools and a methodology to ensure mitigation techniques are left intact and design functionality is preserved.

Analysis and Verfication

Analysis and verification are the most critical pieces for ensuring reliability and availability. Xilinx takes an open and direct approach to assessing SEU FIT. Xilinx stands alone in the publication of radiation effects data for commercial devices, via the Xilinx Device Reliability Report, and uses this data to support pre-design and post-design SEU FIT estimation for reliability and availability analysis.

In order to foster independent verification by interested users and the broader radiation effects community, the SEM IP core optionally provides convenient error injection, a capability enhanced by availability of data files providing a map of Configuration RAM locations essential to a given design’s operation. Further, Xilinx hardware debug tools support device Configuration RAM read back for verification during radiation effects tests.