Vitis HLS

- 设计工具

- Vitis 统一软件平台

- Vitis HLS

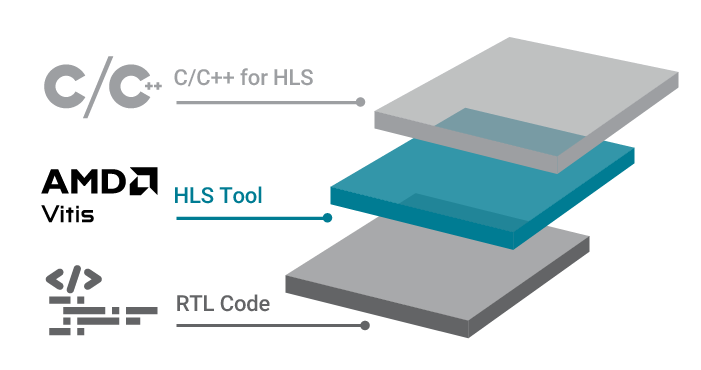

Vitis™ HLS 工具允许用户通过将 C/C++ 函数综合成 RTL,轻松创建复杂的 FPGA 算法。Vitis HLS 工具与 Vivado™ Design Suite(用于综合、布置和布线)及 Vitis™ 统一软件平台(用于所有异构系统设计和应用)高度集成。

- 使用 Vitis HLS 流程,用户可针对 C 代码应用指令,创建专门用于所需实现方案的 RTL。

- 不仅可从 C 语言源代码创建多个设计架构,而且还可启用用于高质量 Correct-by-Construction RTL 的路径。

- C 语言仿真可用于验证设计,支持比基于 RTL 的传统仿真更快的迭代。

- Vitis HLS 工具具有一系列丰富的分析及调试工具,其可促进设计优化。

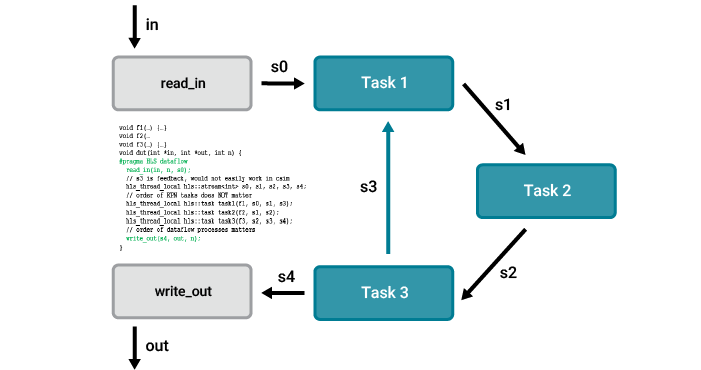

编程模型

Vitis HLS 编程模型

Vitis™ HLS C 语言代码旨在充分利用 AMD FPGA 架构提供的优势和特征。

Vitis HLS 工具支持并行编程构念,可为所需的实现方案建模。这些构念包括:

- 允许流程并行的 HLS 任务

- 允许数据并行的 HLS 矢量

- 允许在并行任务之间进行通信的 HLS 流程

- 综合编译指示可用来控制结果。这些编译指示包括流水线、展开、阵列分区以及接口协议等。

- 如欲了解更多详情,敬请参阅 Vitis 高层次综合用户指南的“HLS 编程人员指南”部分。

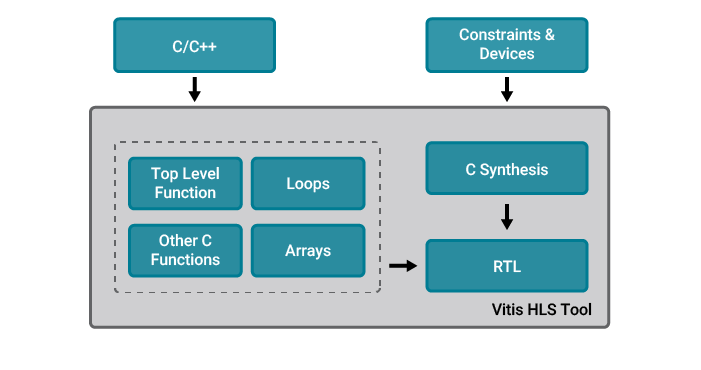

C 至 RTL 的转换

Vitis HLS 工具将对 C 语言代码的不同部分执行不同的综合:

- C/C++ 代码的顶层函数参数不仅可综合成 RTL I/O 端口,而且还可通过接口综合硬件协议自动执行。

- 其它 C 语言函数将综合至 RTL 模块中,保持设计层级。

- C 语言函数循环保持滚动或流水线,以提高性能。

- C 语言代码阵列可指向任何内存资源,如 BRAM、LUTRAM 和 URAM 等。

- 时延、初始化间隔、循环迭代时延和资源利用率等性能指标可使用综合报告查看。

- Vitis HLS 工具的编译指示及优化指令允许配置 C/C++ 代码的综合结果。

C 至 RTL 的综合

仿真和验证

仿真和验证

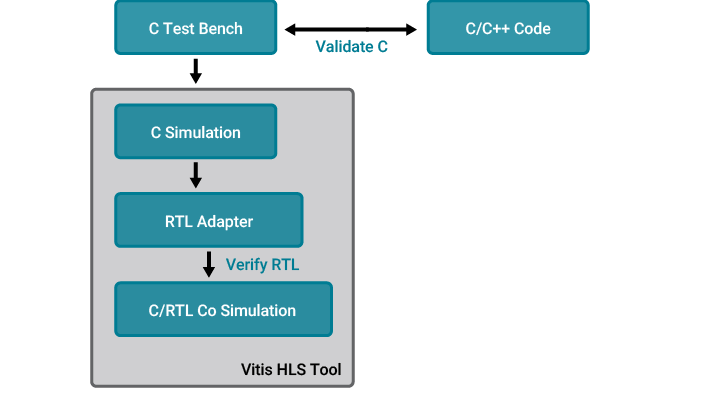

Vitis HLS 工具内建仿真流程,可加速验证进程:

- C 语言仿真将验证 C 代码的功能性。该步骤很快,并会使用 C 语言测试台。

- C/RTL 联合仿真可重复使用 C 语言测试平台,对所生成的 RTL 进行验证:验证 RTL 在功能上是否与 C 语言源代码相同。

- 该流程集成分析、调试和波形查看功能,以及流行的仿真器支持。

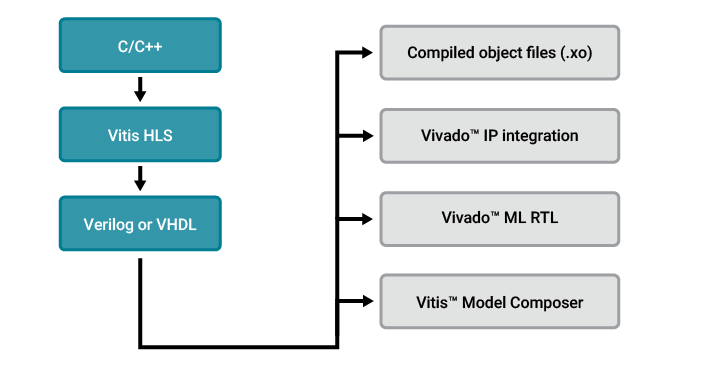

IP 导出

Vitis HLS 工具的输出是一个 RTL 执行方案,其可打包成一个已编译的目标文件 (.xo),也可导出至 RTL IP:

- 编译的目标文件 (.xo) 可用于创建硬件加速函数,用于 Vitis 应用开发流程。

- 该 RTL IP 的使用方式有三种:

- 添加了对 Vivado™ IP Integrator 工具的使用

- 在 Vivado IDE 中作为 RTL 模块导入

- 在 Vitis Model Composer 中作为单个模块集,用于 DSP 应用

IP 导出

2023.2 版本亮点

- 面向 HLS 组件的最新 Vitis™ 统一 IDE

- 最新 Vitis HLS 许可证要求

- 用于在运行 C 综合之前获得性能估计的最新代码分析器特性

- AXI 接口的增强功能:

- HLS AXI Stream 侧通道支持的增强

- 支持用户可配置的 AXI 主机高速缓存

- 其它增强功能:

- 最新代码复杂性报告,可在 C 综合过程中识别设计尺寸问题

- 编译时间缩短:与 2023.1 相比,2023.2 的平均编译时间缩短了 20% *

* 基于 2023 年 8 月 10 日在 1000 个 Vitis L2/L3 代码库设计间的测试,Vitis HLS 版本 2023.2 与 Vitis HLS 2023.1 相比。测试时的系统配置:Intel Xeon E5-2690 v4(2.6GHz CPU)、256GB RAM、RedHat Enterprise Linux 8.6。实际性能会有所不同。系统生产商可能会改变配置,进而会有不同的结果。-VGL-04

2023.1 版本亮点

- 性能提升*:与 2022.2 相比,2023.1 的平均时延缩短了 5.2%

- 在 Vitis HLS 工具中下载、查看和实例化 L1 库函数的简单方法。观看视频

- 在 Vitis HLS 工具中增强了对 AXI 事务处理及猝发报告的支持

*截至 2023 年 2 月 12 日,停止在所有 1208 个 Vitis L1 库 C 代码设计上执行基准测试。所有设计都使用一个支持 2P Intel Xeon E5-2690 CPU 的系统运行,该 CPU 支持 CentOS Linux,启用了 SMT 并禁用了 Turbo Boost。预计硬件配置不会影响软件测试结果。结果可能会因软件及固件设置和配置而异 — VGL-03

2022.2 版本亮点

- 为数据处理应用编写“任务级并行”代码的新方法

- 用户可使用新的 hls::task 函数显式定义任务级并行性

- 为纯设计数据流(例如分组交换)建模更轻松

- 性能与时序增强

- 工具自动推断展开、流水线、阵列分区以及内联编译指示,可提高性能

- 分析与调试增强

- 在所生成的 RTL 代码中从 C 语言来源综合打印语句的新特性

- 仿真 RTL 时,允许跟踪代码模块的执行以及一个变量的值

- 简单易用

-

FFT 和 FIR IP 现在支持 hls::stream 接口

2022.1 版本亮点

- 全新时间线跟踪查看器

- 显示设计中所有幸存函数的运行时配置文件,即那些被转换为模块的函数

- 查看数据流区域在联合仿真后的行为特别实用。原生 Vitis™ HLS — 不再需要启动 xsim 波形查看器

- 全新性能编译指示

- HLS 您的吞吐量目标是使用 #pragma hls 性能

- 如果可能的话,HLS 将尝试使用最少的资源来达标

- HLS 将指示所执行的转换,而且如果不能达标,还将指示限制因素

- 为模块数据流类型提供阵列分区支持

- hls::stream 增强,其中每个元素都是一个阵列

- 可用于将大型阵列处理分解成更小的流水线片段

2021.2 版本亮点

- 用户控制的猝发推断

- 用户可采用新引入的手动猝发优化功能

- 添加一个新的‘hls::burst_maxi’类型来为手动控制猝发行为提供支持 提供全新 HLS API,与新类类型一起使用。

- 在 HLS 设计中,用户需要了解 AXI AMBA 协议和硬件事务处理层面的建模

- 时序与 QoR 增强

- 提高了 HLS 时序估算精度。 当 HLS 报告时序收敛时,Vivado™ RTL 综合也应该预期满足时序要求

- EoU 增强

- 在 C 语言综合报告中添加接口适配器报告

- 用户需要知道接口适配器对其设计的资源影响

- 接口适配器具有可影响设计 QoR 的可变属性

- 在综合报告中添加新章节,以显示编译指示列表和编译指示警告

- 分析与报告增强

- 全新鼠标拖动式缩放功能

- 全新概览特性,不仅可显示全图,而且用户还可放大整体图形的各部位

- 所有函数及环路都与它们的仿真数据一起显示

- 现已在仿真后提供一个新的时间轴跟踪查看器该查看器不仅可显示设计的运行时概况,而且还允许用户保留在 Vitis HLS GUI 中

2021.1 版本亮点

- GUI 中的全新“流程导航器”有助于快速访问流程阶段和报告。环境“综合、分析、调试”视窗合并到一个默认的通用环境中

- BIND_OP 和 BIND_STORAGE 指令的的全新综合报告部分

- 全新的综合后文本报告将反映 GUI 综合报告中提供的信息

- IP 导出和 Vivado™ 实现运行小部件使用各种选项进行重新设计,可将设置和约束文件传递给 Vivado

- 全新函数调用图查看器可查看函数和环路,其可使用可选热图高亮显示,以检查 II、时延或 DSP/BRAM 利用热点

- Versal™ 时序校准以及 DSP 模块本地浮点运算的全新控制(config_op 的 -precision 选项)

- 可替代的可刷新流水线选项已得到改进(自由运行流水线又称“frp”)

- 在 Vitis 中,重塑 m_ax 接口应该通过 hls::vector 类型完成

- s_axilite 和 m_axi 数据存储的全新自定义选项可以是“auto”、“uram”、“bram”或“lutram”,您可以在设计中调整 RAM 利用率

- 在 Vitis 中,为内核引入了一种全新的连续(又称“永不停止”)运行模式

- 已重新设置 axi_lite 辅助时钟选项

INSA Lyon 的 Emeraude 研究团队正在努力为嵌入式音频系统开发新的信号处理技术。该团队使用 AMD Vitis HLS 工具实现了超低时延的音频 DSP 程序。点击这里,进一步了解 Vitis HLS 工具如何帮助该团队在 DSP 至 FPGA 的音频编译过程中实现超低时延。

Customer Case Study

使用 Vitis HLS 实现音频 DSP 至 FPGA 的超低时延

INSA Lyon 的 Emeraude 研究团队正在努力为嵌入式音频系统开发新的信号处理技术。该团队使用 AMD Vitis HLS 工具实现了超低时延的音频 DSP 程序。点击这里,进一步了解 Vitis HLS 工具如何帮助该团队在 DSP 至 FPGA 的音频编译过程中实现超低时延。

Customer Case Study

使用 Vitis HLS 加速设计空间探索

“依我看,AMD Vitis™ HLS 工具的主要优势是设计空间探索特性。您可通过使用优化指令(流水线以及展开等),用适当的时间生成不同的架构及实现方案。如果使用 VHDL/Verilog 手动编码,则无法做到这一点。Vitis HLS 的一个良好特性是可以对 HDL 代码进行联合仿真和验证,以确保 HDL 代码功能正确。”Frank Kesel 博士,德国普福尔茨海姆大学教授

客户案例研究