Analogic’s High-Performance Medical Digital Imaging Detector Technology with Orthogone

Overview

Discover how Orthogone Technologies used the Xilinx Zynq UltraScale+ MPSoC and Artix-7 FPGAs to develop a state-of-the-art digital platform for medical imaging applications that presented many multi-disciplinary technological challenges.

Introduction

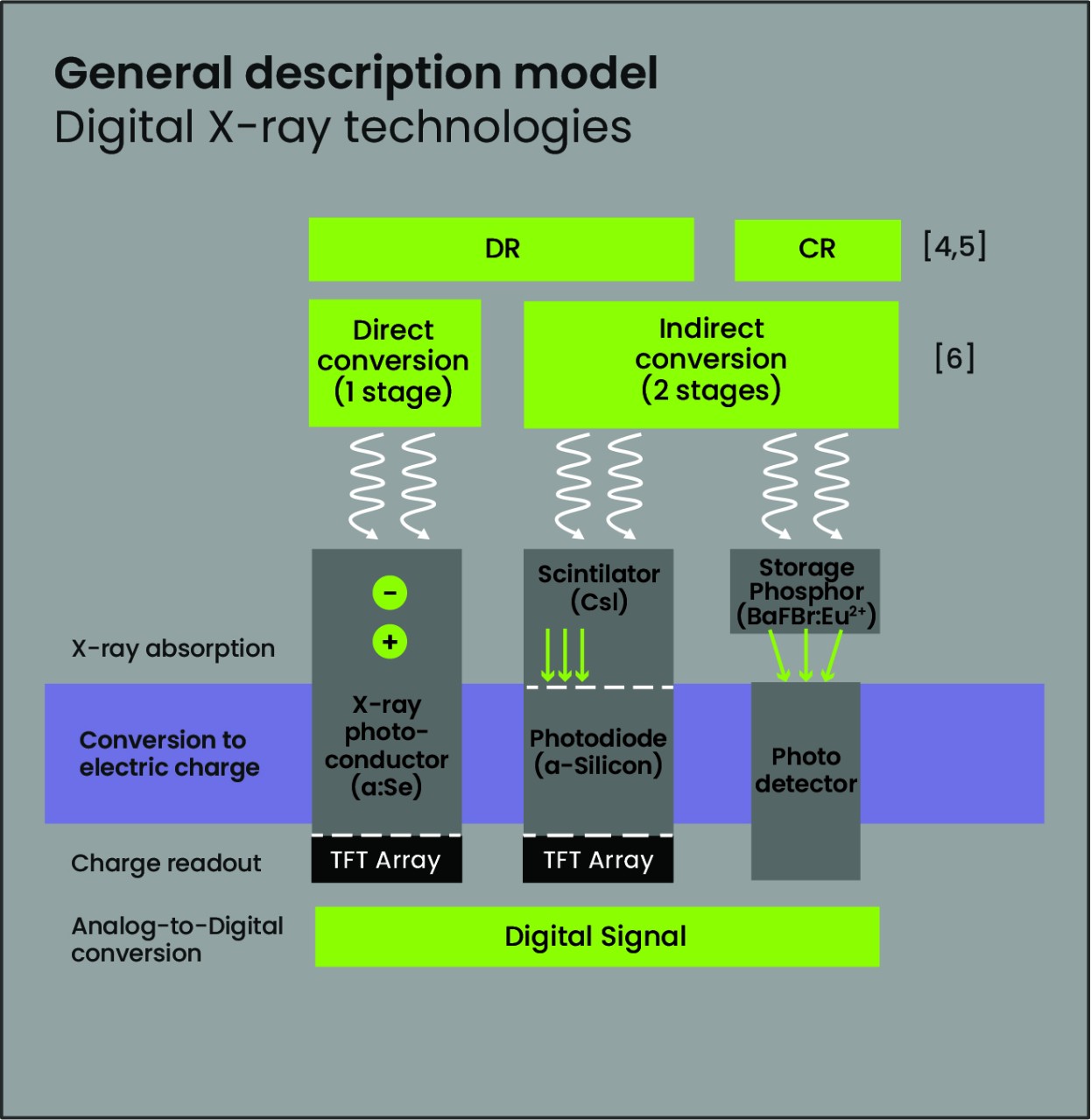

A worldwide leader in direct conversion digital detector technology, Analogic develops and manufactures flat-panel, direct conversion digital detectors used by major medical OEMs in mammography systems. The plates developed by Analogic capture image data directly onto a patented detector made with a layer of amorphous selenium deposited onto a thin-film transistor array. Analogic’s detector technology enables digital tomosynthesis which provides a 3D image for improved reading accuracy and reduced false positives compared to traditional 2D film mammography.

Analogic needed specific technical expertise to allow its patented detection technology to make use of high-performance image processing algorithms. Since Analogic detectors are used by different manufacturers on a range of equipment, the system architecture needed to be designed with versatility and ease of integration as a primary requirement. The Orthogone product development team was brought in as partners to provide needed technical expertise and accelerate the development cycle. Orthogone’s experienced FPGA designers, embedded software designers and hardware designers worked in collaboration with the Analogic team to develop the new detector solution.

Using Xilinx components to overcome technical challenges

Developing a state-of-the-art digital X-ray platform for mammograms, 3D mammography, and other medical imaging applications presented multi-disciplinary technological challenges, including designing a flexible and scalable image reconstruction processing engine that could support multiple sensor configurations.

The team decided to use the Xilinx Zynq UltraScale+ MPSoC for its performance, as well as other Xilinx FPGAs that would provide flexibility and accelerate development time. The easy integration between the software and FPGA into the intuitive bloc design environment with multiple AXI4 interfaces was a key factor in the choice of Xilinx instead of competing technology. As well, the Xilinx evaluation board and reference design helped the team jumpstart the design and derisk most of the design before receiving the PCB.

This article presents the challenges and Xilinx components used in the technical solutions for the multiple parts of the project:

- System design & architecture

- Image processing

- Hardware design

- Software design

System Design & Architecture

To make flat-panel detectors safer for patients, with more accurate readouts, system designers and design architects had to integrate ultra-sensitive sensors with high-speed digital processing functionalities onto a low-profile highly integrated enclosure.

The first step in the image acquisition process is to capture high-speed raw data from the sensor. Depending on the sensor’s resolution and the desired frame rate, it may be required to support readout rates in excess of 10Gbps. A large-area flat panel is often made of multiple sensors that are combined to form a larger high-resolution image. The raw image data is generally transferred from the sensors over multiple high-speed links.

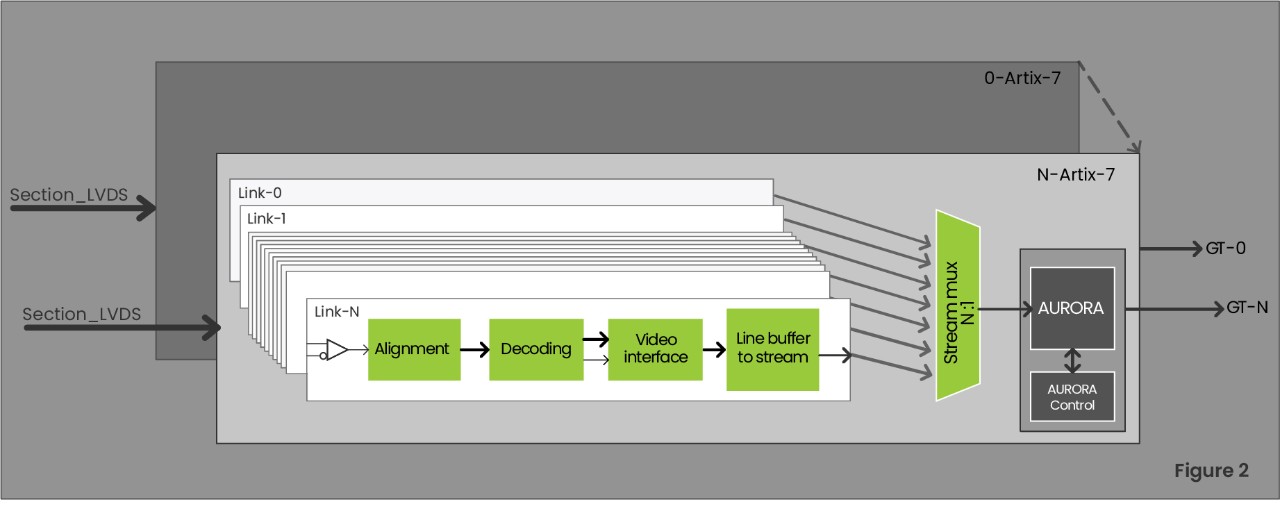

For this application, mammography sensors are divided in multiple independent sections where each one is using multiple high-speed LVDS differential pairs to transfer their raw acquisition data. To avoid running multiple long LVDS links that could cause excessive crosstalk and noise, we opted to transfer raw data to independent low-power Xilinx Artix-7. Using this scheme, we placed each FPGA close to its respective sections, resulting in shorter LVDS links and significantly less PCB routing congestion.

The Artix-7 are installed around an MPSoC located in the center of the PCBA and interface to each of the sections using low-profile connectors and flex cables/PCBs. Each Artix-7 accepts the raw data, decodes the incoming streams, aggregates them and performs data serialization using a Gigabit Transceiver (GT) routed to the MPSoC.

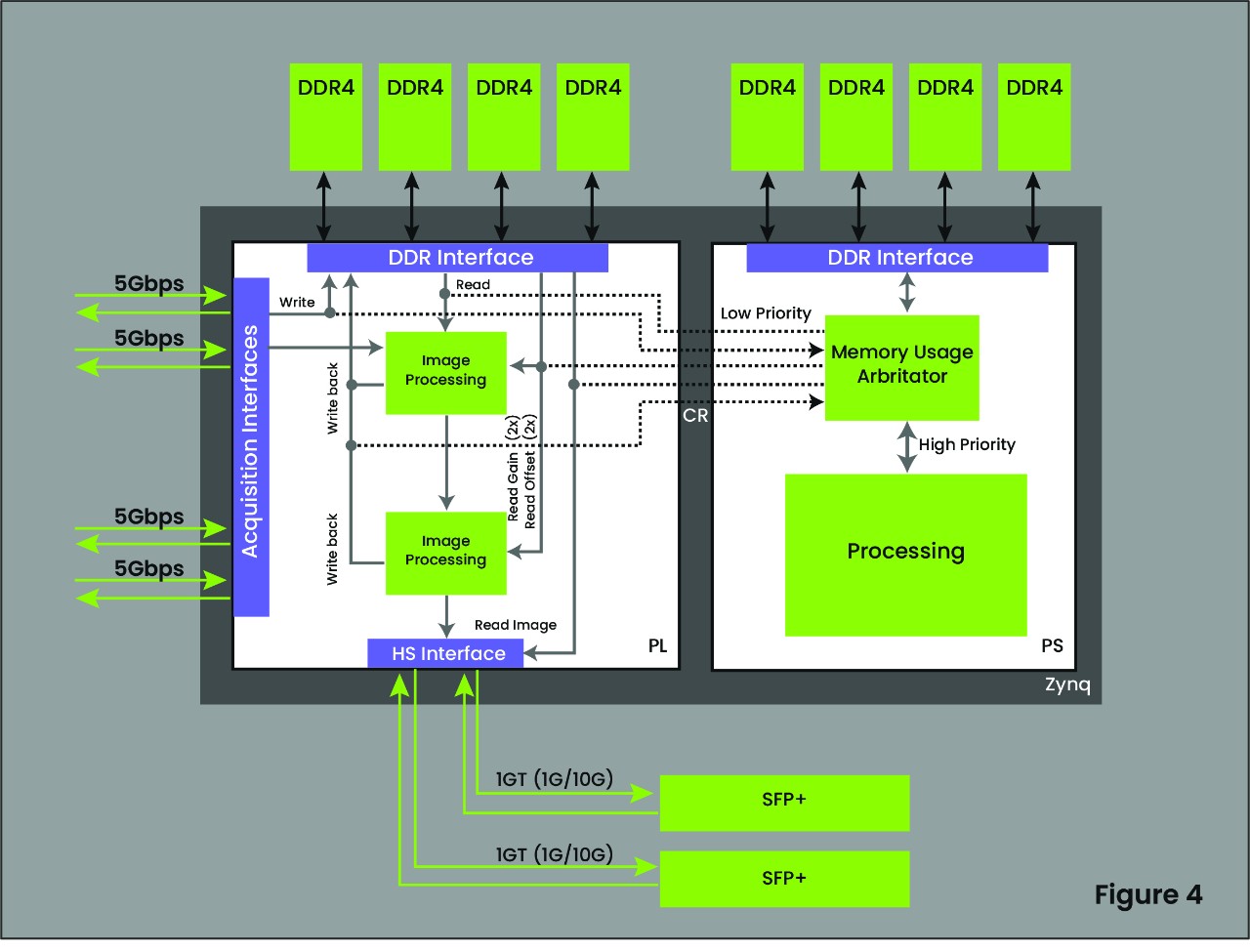

The Xilinx Zync UltraScale+ MPSoC integrates, onto a single device, the Kintex UltraScale+ FPGA programmable fabric with a processing system (PS) that includes a 64-bit dual-core Arm® Cortex®-A53 and a dual-core Arm Cortex-R5. Using a Xilinx MPSoC offers several advantages including the integration of multiple-core ARM processors closely coupled to the FPGA fabric. We chose this architecture to benefit from the FPGA fabric performances and the flexibility of using multiple ARM cores, some of which can be used with operating systems that need to be certified for critical applications required in the healthcare industry. In addition, several high-speed peripheral controllers such as SATA and USB 3.0 are directly integrated into the Zynq MPSoC.

“Since the product will have a relatively long lifetime, it was important to select key components with long-term availability. Xilinx designs products and creates the supporting supply chain with the clear intent to support a minimum 15+ year lifecycle, starting from first production release.” – Alexandre Raymond, CTO, Orthogone Technologies

Image Processing

As mentioned earlier, each of the Artix-7 FPGAs is interfacing to its respective sections. Upon a global trigger signal asserted by the host SW, all sections send their raw data to their respective Artix-7 FPGA.

Each Artix-7 FPGA simultaneously aligns and decodes the incoming data and writes it into a series of line buffers implemented using block RAM (BRAM) memories. The buffered data is next multiplexed and packaged into a single lane 5Gbps Aurora link. The Aurora IP from Xilinx is generated with CRC support to guarantee data integrity. At the other end of the serial link, the receiver flags any transfer with a CRC error and asks for a retry to the Artix-7 FPGA Aurora interface.

Orthogone as designed a scalable architecture to adapt easily different sensor sizes.

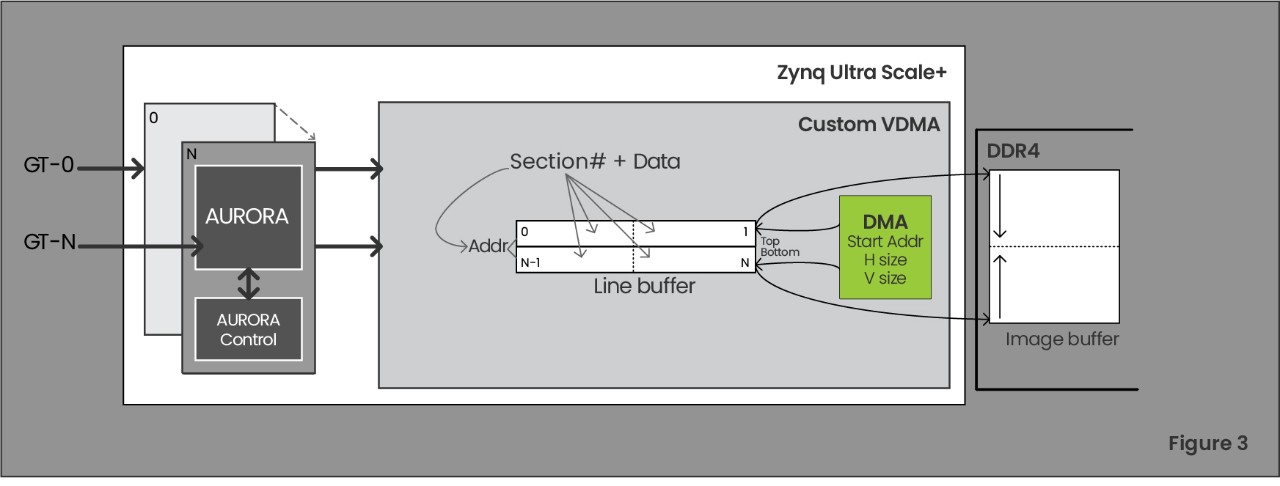

The architecture can accommodate multiple section configurations which makes it very scalable; and the custom VDMA reorganizes the full image in the external memory. Once all the pixels of the image are correctly reordered, the FPGA can perform additional image processing operations to enhance the quality of the image. Fixed pattern noise can be easily removed using flat field correction type processing.

The Xilinx Zynq UltraScale+ MPSoC provides plenty of DSP block resources that can be used to perform image processing on the captured data. The platform uses a ZU7CG MPSoC device that contains 1728 DSP Slices. Each DSP slice fundamentally consists of a dedicated 27 × 18 bit twos complement multiplier and a 48-bit accumulator. Flat field correction and other image processing algorithms can easily be implemented to perform multiplication, addition/subtraction on a frame by frame basis. The processing modules can route the image data to the DDR, or directly to the backend interface that will stream the image/video content on the 10G Ethernet port(s) over a UDP session.

Hardware Design

When designing ultra-high-performance digital X-ray products for the most demanding medical applications, hardware designers are faced with several challenges including minimizing noise, integrating high-speed digital with ultra-low noise circuits, physical dimensions constraints, safety considerations, etc.

A combination of low-noise buck converters and voltage regulators are used to reduce EMI and provide low-noise stable DC rails. The Xilinx Zynq is able to monitor and control all on-board supplies and disable the unnecessary power rails, to lower the power consumption, when required.

The Xilinx Zynq UltraScale+ MPSoC is the heart of the system and is responsible for retrieving the image sensing data coming from the Artix-7 FPGAs and creates the final image to be sent to an external computer connected throughout high-speed optical transceiver interfaces. Local frame buffers are stored in DDR4 memory and are used for reconstruction and frame buffer.

DDR4 was chosen for speed and power consumption and all calibration required is done automatically by the Xilinx MIG. The DDR4 memory has been architected to support acquisition at a very fast frame rate with multiple frame (images/coefficients) movements.

There are several boot mode possibilities for the Xilinx Zynq UltraScale+ FPGA, this board is configured for QSPI32 and JTAG (for development and debug purposes). The QSPI Flash is connected to the PS side of the Zynq which will boot from there and program the FPGA. The QSPI Flash contains FPGA bitfiles and software boot code. A second QSPI Flash is used to log errors and other information.

An SSD drive is also present on the SATA interface of the PS. This drive contains the different applications running on each processor (Linux, MEL, real-time), backup FPGA bitfiles, and detector configuration.

Software Design

Analogic’s detector software running in the Zynq UltraScale+ hardware platform is split into different applications. Those applications manage real-time control of the image datapath in the FPGA side and also non-critical background tasks with Linux.

The Zynq MPSoC hardware platform uses multiple processors that have access to private and shared memory regions and peripherals. Based on the Mentor® Embedded Multicore Framework (MEMF) library, most inter processor messaging goes through system shared memory. It uses a mechanism called "rpmsg" that has been developed for multi-processor systems. This mechanism uses interrupts and shared memory for receiving and transmitting messages between multiple processors.

Results

Through innovative design and use of technology, Orthogone worked in partnership with Analogic to develop a solution that has the versatility and ease of use required to maintain its competitive edge over extended product life cycles. To learn more about partnering with Orthogone, see Outsourcing Engineering Services.

Arm and Cortex are registered trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere.

Mentor is a registered trademark of Mentor Graphics Corporation.

About Alexandre Raymond

Alexandre Raymond serves as Chief Technology Officer (CTO) at Orthogone Technologies. In this role, he is responsible for driving the vision of Orthogone’s research and development activities as well as the development of technologies and intellectual property in collaboration with Orthogone’s clients.